# Space-Efficient Simulation of Quantum Computers

47<sup>th</sup> ACM Southeast Conference, Clemson, SC March 19-21, 2009 (Session F3, Systems)

Michael P. Frank<sup>1</sup>, Uwe H. Meyer-Baese<sup>1</sup>, Irinel Chiroescu<sup>2</sup>, Liviu Oniciuc<sup>1</sup>, Robert A. van Engelen<sup>3</sup> <sup>1</sup>Dept. of Elec. & Comp. Eng., FAMU-FSU College of Engineering <sup>2</sup>National High Magnetic Field Laboratory, Florida State University <sup>3</sup>Department of Computer Science, Florida State University

# **Abstract (for reference)**

Traditional algorithms for simulating quantum computers on classical ones require an exponentially large amount of memory, and so typically cannot simulate general quantum circuits with more than about 30 or so qubits on a typical PC-scale platform with only a few gigabytes of main memory. However, more memory-efficient simulations are possible, requiring only polynomial or even linear space in the size of the quantum circuit being simulated. In this paper, we describe one such technique, which was recently implemented at FSU in the form of a C++ program called SEQCSim, which we releasing publicly. We also discuss the potential benefits of this simulation in quantum computing research and education, and outline some possible directions for further progress.

# What is a Quantum Computer?

- □ A new, more powerful fundamental paradigm for computing within the laws of physics.

- Apparently exponentially faster on some problems.

- Some key differences between Classical vs. Quantum Computation:

- State representations:

- **Classical:** A sequence of *n* bit values,  $w \in \mathbf{B}^n$ , where  $\mathbf{B} = \{0,1\}$ .

- **Quantum:** A function  $\Psi \in \mathbf{H}$ , where  $\mathbf{H} = \mathbf{B}^n \to \mathbf{C}$ , mapping classical states to complex numbers ("amplitudes").

- Logic operators ("gates"):

- **Classical:** A function from several bits to one bit,  $g: \mathbf{B}^k \to \mathbf{B}$

- **Quantum:** A unitary (invertible, length-preserving) linear transformation  $U: \mathbf{S} \to \mathbf{S}$ , where  $\mathbf{S} = \mathbf{B}^k \to \mathbf{C}$ .

- Measurement of computation results:

- **Classical:** Measured value is exactly determined by machine state.

- **Quantum:** Probability of measuring state as being *w* is  $\propto |\Psi(w)|^2$ .

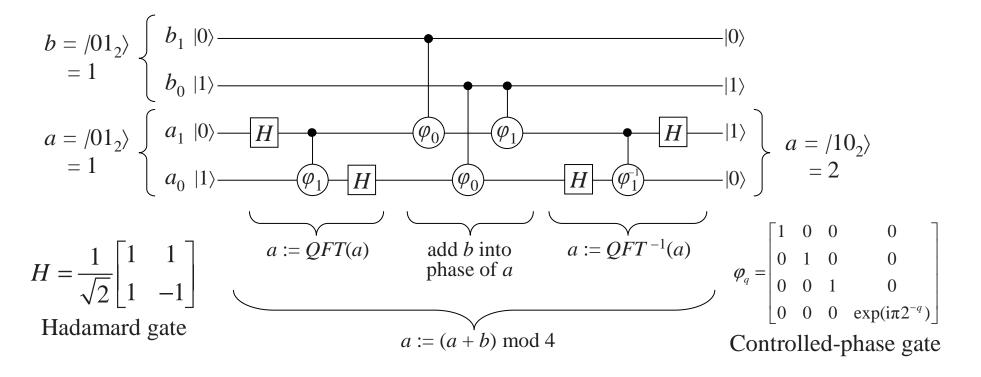

## A Simple Quantum Circuit: Draper Adder

**FAMU-FSU College of Engineering**

Uses the quantum Fourier transform (QFT) and its inverse QFT<sup>-1</sup> to add two 2-bit input integers in a temporary phase-based representation. Here it is computing 1 + 1 = 2.

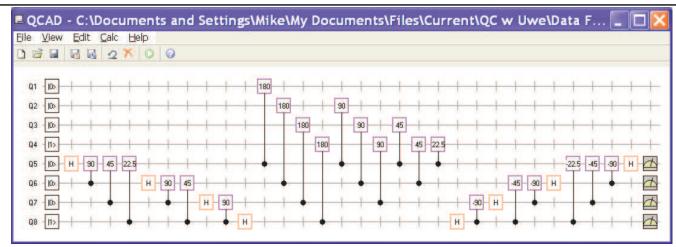

# A Larger Draper Adder (2×4 bits)

QCAD tool, by Hiroshi Watanabe, University of Tokyo, available from http://apollon.cc.u-tokyo.ac.jp/~watanabe/qcad/index.html

- □ Some advantages of the Draper adder:

- Minimal quantum space usage: Requires no ancilla bits for carries.

- A good simple, but nontrivial example of a quantum algorithm.

- □ A disadvantage of the Draper adder:

- Slow; requires  $\Theta(n^2)$  gates for an *n*-bit add!

- □ Unlikely to be used in practice, unless qubits are very expensive.

## Some Potential Applications of Quantum Computers

- □ If quantum computers of substantial size are built, known quantum algorithms can be applied to obtain:

- Polynomial-time cryptanalysis of popular public-key cryptosystems (*e.g.*, RSA).

- Polynomial-time simulations of quantum-mechanical physical systems.

- Square-root speedups of simple unstructured searches of computed oracle functions.

- And not a whole lot else!

- A much wider variety of interesting & useful quantum algorithms is needed,

- But new quantum algorithms are difficult to develop.

- Need flexible, capabable simulation tools for design validation.

## A Problem with Nearly All Existing Quantum Computer Simulators

- □ They require *exponential space* as the number of bits in the simulated computer increases.

- Why: They update a *state vector* explicitly representing the full wavefunction  $\Psi: \mathbf{B}^n \to \mathbf{C}$ .

- $\Box$  This vector contains  $2^n$  complex numbers

- 1 for each possible configuration of the machine's *n* bits

- If the available memory holds  $1G(2^{30})$  numbers,

- □ We can only simulate <30-bit quantum computers!

- The large space usage also imposes a significant slowdown to access main memory or disk.

# **A Way to Solve This Problem**

- □ We can reformulate quantum mechanics in an equivalent framework *without state vectors*.

- Feynman (1942): Any desired amplitude can be computed using a *path integral* expression summing over possible *classical* trajectories.

- Bohm (1952): Can maintain a *classical* state that evolves under the influence of only wavefunction amplitudes in the immediate neighborhood.

- □ The only real requirement is to obtain the right probability of arriving at each final state!

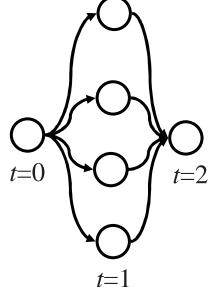

## A Complexity Theorist's View of Feynman's Path Integral

- □ Consider any computation with a wide dataflow graph (uses more space than time)

- The graph at right uses 4 variables at time *t*=1, but only takes 2 steps.

- We can make the algorithm more space-efficient by recomputing intermediate variables dynamically when needed, instead of storing them.

Bernstein & Vazirani, 1993: Can apply this generic tradeoff to simulating quantum computers (duh).

## **SEQCSim:** The <u>Space-Efficient</u> <u>Quantum Computer Simulator</u>

- □ Core idea was conceived circa 2002 at UF.

- Adding Bohm updates to Feynman recursion.

Avoids having to enumerate all possible final states.

- □ A working C++ software prototype was developed and demonstrated at FSU in 2007.

- Future versions of the simulator will have a more expressive programming interface.

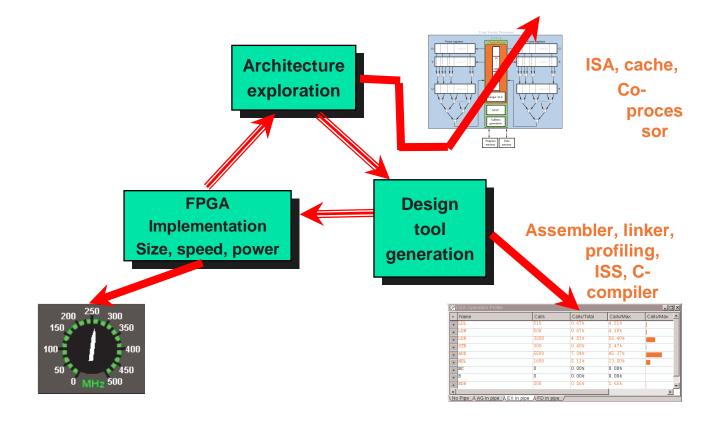

- A performance-optimized FPGA-based implementation is currently being developed.

### **SEQCSim Input Files** for 2×2-Bit Draper Adder

| qconfi | ig.txt | form | nat v  | ers | sion  | 1  |

|--------|--------|------|--------|-----|-------|----|

| bits:  | 4      | Dec  | lare 1 | eg  | giste | ſS |

| named  | bitarı | ray: | a[2]   | @   | 0     |    |

| named  | bitarı | ray: | b[2]   | @   | 2     |    |

qinput.txt format version 1

a = 1

b = 1

Input values to add

| <b>qoperators.txt</b> format version 1         |                                                                  |  |  |  |  |

|------------------------------------------------|------------------------------------------------------------------|--|--|--|--|

| operators: 4                                   |                                                                  |  |  |  |  |

| operator #: 0                                  | Quantum circuit (gate application sequence)                      |  |  |  |  |

| name: H                                        | Quantum circuit (gate application sequence)                      |  |  |  |  |

| size: 1 bits qops                              | seq.txt format version 1                                         |  |  |  |  |

| matrix: open                                   | rations: 9                                                       |  |  |  |  |

| (0.7071067812 + i*0)(0.7071067812 + i*0) open  | ration #0: apply unary operator H to bits a[1]                   |  |  |  |  |

| (0.7071067812 + i*0)(-0.7071067812 + i*0) open | ration #1: apply binary operator cPiOver2 to bits a[1], a[0]     |  |  |  |  |

| operator #: 1 Operator                         | operation #2: apply unary operator H to bits a[0]                |  |  |  |  |

| name: cZ Gate open                             | ration #3: apply binary operator cZ to bits b[1], a[1]           |  |  |  |  |

| size: 2 bits definitions oper                  | ration #4: apply binary operator cZ to bits b[0], a[0]           |  |  |  |  |

|                                                | ration #5: apply binary operator cPiOver2 to bits b[0], a[1]     |  |  |  |  |

| (1 + i*0) (0 + i*0) (0 + i*0) (0 + i*0) open   | ration #6: apply unary operator H to bits a[0]                   |  |  |  |  |

| (0 + i*0) (1 + i*0) (0 + i*0) (0 + i*0) open   | ration #7: apply binary operator inv_cPiOver2 to bits a[1], a[0] |  |  |  |  |

| (0 + i*0) (0 + i*0) (1 + i*0) (0 + i*0) open   | ration #8: apply unary operator H to bits a[1]                   |  |  |  |  |

| (0 + i*0) (0 + i*0) (0 + i*0) (-1 + i*0)       |                                                                  |  |  |  |  |

| (two additional operators elided for brevity)  |                                                                  |  |  |  |  |

## **SEQCSim Core Algorithm**

#### // Bohm-inspired iterative state updating.

procedure SEQCSim::run():

curState := inputState; // Current basis state // Current amplitude curAmp := 1;for PC =: 0 to #gates, // Current gate index (w.r.t. gate[*PC*] operator and its operands,) for each neighbor *nbri* of *curState*, if *nbri* = *curState*, *amp*[*nbri*] :=*curAmp*; else *amp*[*nbri*] := calcAmp(*nbri*); amp[] := opMatrix \* amp[]; // Matrix prod. // Calculate probabilities as normalized // squares of amplitudes. prob[] := normSqr(amp[]); // Pick a successor of the current state. *i* := pickFromDist(*prob*[]); curState := nbri; curAmp := amp[nbri].

// Feynman-inspired recursive

// amplitude-calculation procedure.

function SEQCSim::calcAmp(Neighbor nbr): curState := nbr; if PC=0 return (curState = inputState) ? 1 : 0; (w.r.t. gate[PC-1] operator and its operands,) for each predecessor predi of curState, PC := PC - 1; amp[predi] = calcAmp(predi); PC := PC + 1; amp[] := opMatrix \* amp[]; return amp[curState];

Complete C++ console app has 24 source files, total size 115 KB

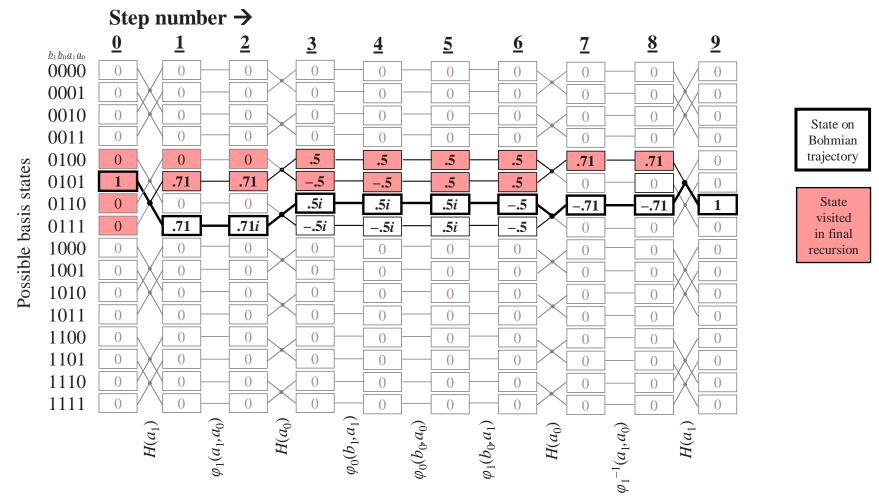

### **Illustration of SEQCSim Operation on 2×2-Bit Draper Adder**

# **Complexity Analysis**

- □ Defining the following parameters:

- a = const. = max. arity of quantum gates

- s = width (# of qubits) in simulated circuit

- t = time (# of operations) in simulated circuit

- k(< t) = # of *nontrivial* operations in sim'd circ.

- □ For a moderately well-optimized implementation of SEQCSim, we can have

- Space complexity: O(s + t)Time complexity:  $O(s + t \cdot 2^{ak})$

### SEQCSim Output on 2×2-Bit Draper Adder

```

Welcome to SEQCSIM, the Space-Efficient Quantum Computer SIMulator.

(C++ console version)

By Michael P. Frank, Uwe Meyer-Baese, Irinel Chiorescu, and Liviu Oniciuc.

Copyright (C) 2008 Florida State University Board of Trustees.

All rights reserved.

SEQCSim::run(): Initial state is 3->0101<-0 (4 bits) ==> (1 + i*0).

SEQCSim::Bohm_step_forwards(): (tPC=0)

The new current state is 3 - 0111 < 0 (4 bits) ==> (0.707107 + i*0).

SEQCSim::Bohm step forwards(): (tPC=1)

The new current state is 3 \rightarrow 0111 < 0 (4 bits) ==> (0 + i*0.707107).

... (5 intermediate steps elided for brevity) ...

SEQCSim::Bohm_step_forwards(): (tPC=7)

The new current state is 3 \rightarrow 0110 < -0 (4 bits) ==> (-0.707107 + i*0).

SEQCSim::Bohm step forwards(): (tPC=8)

The new current state is 3 \rightarrow 0110 < 0 (4 bits) ==> (1 + i*0).

SEQCSim::done(): The PC value 9 is >= the number of operations 9.

-1+1 = 2 = 10_{2}

We are done!

```

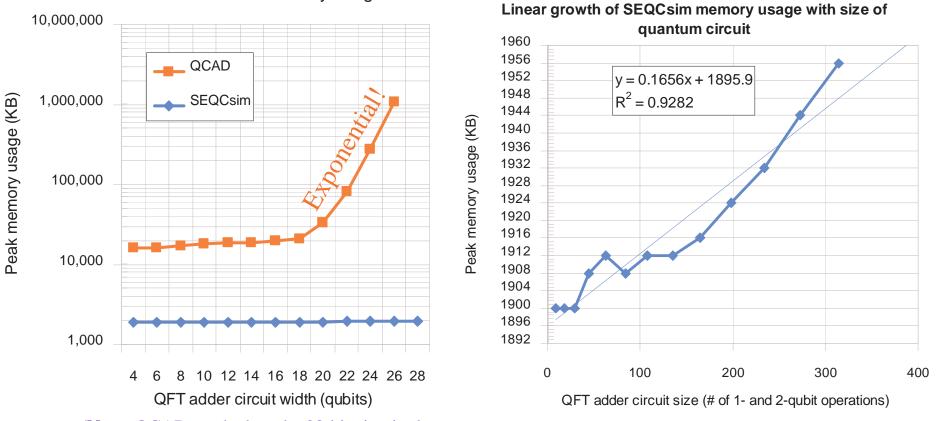

### **Empirical Measurements** of Space Complexity

QCAD vs. SEQCsim memory usage

(Note: QCAD crashed on the 28-bit circuit, due to insufficient memory available on the test PC.)

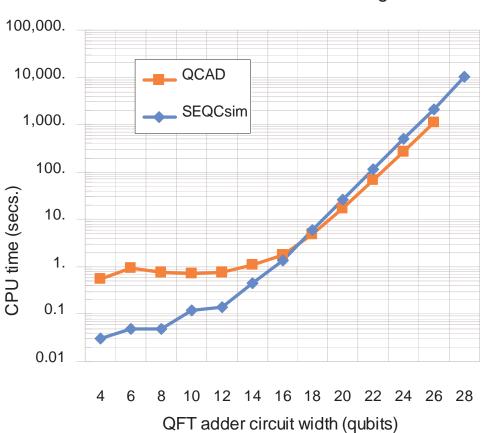

### **Empirical Measurements** of CPU Time Utilization

- SEQCSim is 10× faster than QCAD on small circuits

- This is probably largely because QCAD has a GUI and SEQCSim doesn't.

- SEQCSim is ~2× slower than QCAD on large circuits.

- But there is much room for improvement.

- □ Take better advantage of available memory.

- Reimplement in specialpurpose hardware

QCAD vs. SEQCsim CPU time usage

### **FPGA Tools (1 of 5): Altera SOPC Builder**

| 🗎 Altera SOPC Builder       | □      | t                 | Clock              | Settings                    |           |                     |              |                                        |

|-----------------------------|--------|-------------------|--------------------|-----------------------------|-----------|---------------------|--------------|----------------------------------------|

|                             | Device | Family:           | yclone II          | Name                        | Source    |                     | MHz          | Add                                    |

| ⊕ Bridges and Adapters      |        | i anny.p          | cik_               | 1 Ext                       | ernal     | 50.0                |              | . <u>Auu</u>                           |

|                             |        |                   | -                  | I.                          |           | 1                   |              | Remove                                 |

|                             |        |                   |                    |                             |           |                     |              |                                        |

|                             |        |                   |                    |                             |           |                     |              |                                        |

| ⊕ High Speed                |        |                   |                    |                             |           |                     |              |                                        |

| ⊕-PCI                       | Use    | Conne             | Module Name        | Description                 | Clock     | Base                | End          | IRQ                                    |

|                             |        |                   | 🗖 cpu_0            | Nios II Processor           |           |                     |              |                                        |

| Avalon-ST JTAG I            |        |                   | instruction_master | Avalon Memory Mapped Master | clk_1     |                     |              |                                        |

| 🔍 Avalon-ST Serial I        |        | $  \sim$          | data_master        | Avalon Memory Mapped Master |           | IRQ                 | D IRQ 31←    | $\neg$                                 |

| ·····   JTAG UART           |        | $ \searrow $      | jtag_debug_module  | Avalon Memory Mapped Slave  |           | ■ 0x01002800        | 0x01002fff   |                                        |

| ISPI (3 Wire Serial)        |        |                   | onchip_memory2_0   | On-Chip Memory (RAM or ROM) |           |                     |              |                                        |

| IUART (RS-232 Se            |        | $ \rightarrow $   | s1                 | Avalon Memory Mapped Slave  | cik_1     | ■ 0x01001000        | 0x01001fff   |                                        |

| Legacy Components           |        |                   | Switches           | PIO (Parallel I/O)          |           |                     |              |                                        |

| -Memories and Memory Contro |        | $  \rightarrow$   | s1                 | Avalon Memory Mapped Slave  | cik_1     |                     | 0x0100302f   |                                        |

| ⊕ ··DMA                     |        |                   | 🗆 LEDs             | PIO (Parallel I/O)          |           |                     |              |                                        |

| ⊞⊸Flash                     |        | $  \rightarrow$   | s1                 | Avalon Memory Mapped Slave  | cik_1     | <b>₽ 0x01003030</b> | 0x0100303f   |                                        |

| ⊡On-Chip                    |        |                   | 🖂 jtag_uart_0      | JTAG UART                   |           |                     |              |                                        |

| Avalon-ST Dual C            |        | $  \rightarrow$   | avalon_jtag_slave  | Avalon Memory Mapped Slave  | clk_1     | <b>₽ 0x01003040</b> | 0x01003047 - | jā                                     |

| Avalon-ST Multi-C           |        |                   | 🗆 sdram_0          | SDRAM Controller            |           |                     |              | T                                      |

| 🔍 Avalon-ST Round 🗾         |        | $\hookrightarrow$ | s1                 | Avalon Memory Mapped Slave  | cik_1     |                     | 0x00ffffff   |                                        |

|                             |        |                   | sys_clk_timer      | Interval Timer              |           |                     |              |                                        |

|                             |        | $\hookrightarrow$ | s1                 | Avalon Memory Mapped Slave  | cik_1     |                     | 0x0100301f   | —————————————————————————————————————— |

|                             |        |                   |                    |                             | . –       |                     |              |                                        |

|                             | 1      |                   | [                  | 1                           |           |                     |              |                                        |

| New Edit Add                |        |                   | Remove Edit        | 🔺 Move Up 🛛 🤝               | Move Down | Address Map         | Filter       |                                        |

|                             |        |                   |                    |                             |           |                     |              |                                        |

### **FPGA Tools (2 of 5): NIOS II Soft-Core Configuration**

| 😐 Nios II Processor - c                                                                      | :pu_0                           |                                                                                                  |                                                                                                                                                               | ×                                      |

|----------------------------------------------------------------------------------------------|---------------------------------|--------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| Settings                                                                                     |                                 |                                                                                                  |                                                                                                                                                               |                                        |

| Core Nios II Cach                                                                            | ies and Memory Interfaces $>$   | Advanced Features $ ightarrow$ 1                                                                 | MMU and MPU Settings > JTA                                                                                                                                    | G Debug Module > Custom Instructions > |

| Core Nios II                                                                                 | í                               |                                                                                                  | í                                                                                                                                                             |                                        |

| Select a Nios II core:                                                                       |                                 |                                                                                                  |                                                                                                                                                               |                                        |

|                                                                                              | ○Nios II/e                      | ○Nios II/s                                                                                       | ⊙Nios II/f                                                                                                                                                    |                                        |

| Nios II<br>Selector Guide<br>Family: Cyclone II<br>f <sub>system:</sub> 50.0 MHz<br>cpuid: 0 | RISC<br>32-bit                  | RISC<br>32-bit<br>Instruction Cache<br>Branch Prediction<br>Hardware Multiply<br>Hardware Divide | RISC<br>32-bit<br>Instruction Cache<br>Branch Prediction<br>Hardware Multiply<br>Hardware Divide<br>Barrel Shifter<br>Data Cache<br>Dynamic Branch Prediction |                                        |

| Performance at 50.0 MH:                                                                      | z Up to 5 DMIPS                 | Up to 25 DMIPS                                                                                   | Up to 51 DMIPS                                                                                                                                                |                                        |

| Logic Usage                                                                                  | 600-700 LEs                     | 1200-1400 LEs                                                                                    | 1400-1800 LEs                                                                                                                                                 |                                        |

| Memory Usage                                                                                 | Two M4Ks (or equiv.)            | Two M4Ks + cache                                                                                 | Three M4Ks + cache                                                                                                                                            |                                        |

| Hardware Muttiply: Emb                                                                       |                                 | Hardware Divide                                                                                  |                                                                                                                                                               |                                        |

|                                                                                              | nory: sdram_0                   | ✓ Offset: 0×0                                                                                    | 0×00800                                                                                                                                                       | 0000                                   |

| Exception Vector: Mem                                                                        | <sup>ory:</sup> sdram_0         | Offset: 0x20                                                                                     | 0×00800                                                                                                                                                       | 020                                    |

| Include MMU                                                                                  | hen using an operating system t | hat explicitly supports an MMI                                                                   | 1                                                                                                                                                             |                                        |

| Fast TLB Miss Exception                                                                      |                                 |                                                                                                  | offset: <sub>0x0</sub>                                                                                                                                        |                                        |

| 🔲 Include MPU                                                                                | 1                               |                                                                                                  | Jone -                                                                                                                                                        |                                        |

|                                                                                              |                                 |                                                                                                  |                                                                                                                                                               |                                        |

|                                                                                              |                                 |                                                                                                  |                                                                                                                                                               |                                        |

|                                                                                              |                                 |                                                                                                  |                                                                                                                                                               |                                        |

|                                                                                              |                                 |                                                                                                  |                                                                                                                                                               | Cancel < Back Next > Finish            |

|                                                                                              |                                 |                                                                                                  |                                                                                                                                                               |                                        |

# **FPGA Tools (3 of 5):**

#### **Custom Hardware Generation with C2H**

| Nios II C/C++ - dma_c2h_tutorial.c<br>File Edit Refactor Navigate Search |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | _ 🗆 ×                                                                                                                                                            |

|--------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ] 📬 • 🔛 📥   🚠   🎯 • 🚳 •                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 🔛 🔣 Nios II C/C++                                                                                                                                                |

| Nios II C/C++ Proj 🛛 🗖 🗖                                                 | ⓓ dma_c2h_tutorial.c 🛛 🗧                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Cutline 🛛 🗖 🗖                                                                                                                                                    |

| <pre></pre>                                                              | <pre>#include <stdio.h> #include <stdio.h> #include <string.h> #include <sys alt_cache.h=""> #include "sys/alt_alarm.h" #define TRANSFER_LENGTH 1048576 #define ITERATIONS 100 #define Switches (volatile char *) 0x01003020 #define LEDs (char *) 0x01003030 int do_dms( int * _restrict_ dest_ptr, int * _restrict_ source_ptr, int length {     int i;     for( i = 0; i &lt; (length &gt;&gt; 2); i++ ) } </sys></string.h></stdio.h></stdio.h></pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Stdio.h     Stdio.h     String.h     Sys/alt_cache.h     Sys/alt_alarm.h     TRANSFER_LENGTH     TTEDATIONS     Make Targets      OMA_tutor     DMA_tutor_syslib |

| application.stf                                                          | Problems Console Properties C2H X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Refresh 🏠 ← →  🗖 🗖                                                                                                                                               |

| E - Countration (nios_system)                                            | Flotens Conside Properties Control Problems Conside Properties Control Use software implementation for all accelerators Use the existing accelerators Analyze all accelerators Build software and generate SOPC Builder system Build software and generate SOPC Builder system Build software accelerator in place of software implementation. Flush data cache before each call. Use hardware accelerator in place of software implementation Use hardware accelerator in place of software implementation Use software implementation W use software implementation |                                                                                                                                                                  |

|                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                  |

| ] □◆                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                  |

### **FPGA Tools (4 of 5): LISA Processor Design Cycle**

### **FPGA Tools (5 of 5): LISA Development Tools**

|                                       | asm"                                                                                                                                                                                         |                                                                                                                                  | - <b>D</b> × |                                                                                                                                                                                                                                                                                                         |                                          |                                                                                                                |                                                                                                     |                                                                                                                          |

|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| [000000                               |                                                                                                                                                                                              |                                                                                                                                  |              | Memories<br>Memories                                                                                                                                                                                                                                                                                    |                                          |                                                                                                                | × Source Fil                                                                                        | es                                                                                                                       |

| 000000 🔁                              | D1]: NOP                                                                                                                                                                                     |                                                                                                                                  |              |                                                                                                                                                                                                                                                                                                         | lemory Range: 0x0000000                  | 0. 0×000000ff                                                                                                  | Files                                                                                               |                                                                                                                          |

| 0000000 (D000000                      | ; R[2] has pointer to cos<br>D2]: LDL R[2], #( h0 & Oxff)                                                                                                                                    | efficients operands                                                                                                              |              | Si Si                                                                                                                                                                                                                                                                                                   | ize: 00000100, Native Bits               | ze: 16                                                                                                         | Sea 🗠 🧰 Sea                                                                                         | rch Director                                                                                                             |

| (000000                               | D3]: LDH R[2], #(h0 >> 8)                                                                                                                                                                    |                                                                                                                                  |              | Er<br>Address 0                                                                                                                                                                                                                                                                                         | ndianess, Native: little, Dis<br>1 2 3 4 | play: little                                                                                                   |                                                                                                     | embly Files                                                                                                              |

| 2 [000000                             | ; R[3] is pointer to x da<br>D4]: LDL R[3], #( x0 & Oxff)                                                                                                                                    | ata array                                                                                                                        |              | 0000000000 00001 00                                                                                                                                                                                                                                                                                     |                                          |                                                                                                                |                                                                                                     | der Files                                                                                                                |

| • <u> </u>                            | 05]: LDH R[3], #(_x0 >> 8)                                                                                                                                                                   |                                                                                                                                  |              | 000000008 00040 00                                                                                                                                                                                                                                                                                      |                                          |                                                                                                                |                                                                                                     | ++ Files                                                                                                                 |

| 1000000                               |                                                                                                                                                                                              |                                                                                                                                  |              | 000000016 00000 00                                                                                                                                                                                                                                                                                      | 0000                                     | 00000                                                                                                          |                                                                                                     |                                                                                                                          |

| 172                                   |                                                                                                                                                                                              |                                                                                                                                  |              | 000000024 00000 00                                                                                                                                                                                                                                                                                      |                                          | 00000                                                                                                          | ·                                                                                                   |                                                                                                                          |

| 000000                                | ; R[4]=R[4]+ &R[3]++<br>MAC R[4], R[3], R[2]                                                                                                                                                 | * &R[2]++                                                                                                                        |              |                                                                                                                                                                                                                                                                                                         | Mem                                      | <b>Ory</b>                                                                                                     |                                                                                                     |                                                                                                                          |

| 000000                                | 09]: MAC R[4], R[3], R[2]                                                                                                                                                                    |                                                                                                                                  |              |                                                                                                                                                                                                                                                                                                         |                                          |                                                                                                                | Files (S                                                                                            | ymbols_/                                                                                                                 |

| [000000                               | Da]: MAC R[4], P(2) P(0)                                                                                                                                                                     |                                                                                                                                  |              |                                                                                                                                                                                                                                                                                                         |                                          |                                                                                                                |                                                                                                     |                                                                                                                          |

|                                       | ; Test progra                                                                                                                                                                                | 1.1                                                                                                                              |              |                                                                                                                                                                                                                                                                                                         | moni                                     | 10r 00000                                                                                                      | Name                                                                                                | Valu                                                                                                                     |

| 000000]                               |                                                                                                                                                                                              | assemble                                                                                                                         |              |                                                                                                                                                                                                                                                                                                         | 0000                                     | 00000                                                                                                          | EPC                                                                                                 | 12                                                                                                                       |

| 000000                                | Dd]: NOP                                                                                                                                                                                     |                                                                                                                                  | - LI         |                                                                                                                                                                                                                                                                                                         |                                          |                                                                                                                | APC                                                                                                 | 13                                                                                                                       |

| [000000]                              | De]: NOP                                                                                                                                                                                     |                                                                                                                                  | _ 1          |                                                                                                                                                                                                                                                                                                         |                                          | 1 000001 000001 000001                                                                                         | + FPC                                                                                               | 14                                                                                                                       |

|                                       |                                                                                                                                                                                              | -                                                                                                                                |              | •                                                                                                                                                                                                                                                                                                       |                                          | •                                                                                                              | I PRC                                                                                               | 0                                                                                                                        |

| X Disassembly                         |                                                                                                                                                                                              |                                                                                                                                  |              | data mem (proq mer                                                                                                                                                                                                                                                                                      | m_/                                      | <u> </u>                                                                                                       | BPC BPC vali                                                                                        | 1 0                                                                                                                      |

|                                       |                                                                                                                                                                                              |                                                                                                                                  |              | data mem Aproq mer                                                                                                                                                                                                                                                                                      |                                          | <u>&gt;</u>                                                                                                    | BPC_vali                                                                                            |                                                                                                                          |

| 🗶 Disassembly                         | s Address Instruction                                                                                                                                                                        | Disassembly                                                                                                                      | ×            | data mem A proq mer                                                                                                                                                                                                                                                                                     |                                          |                                                                                                                | BPC_vali                                                                                            | 1 0                                                                                                                      |

| X Disassembly<br>Disassembly          | s Address Instruction<br>[00000001] 00000                                                                                                                                                    | Disassembly<br>NOP                                                                                                               | ×            | data mem A proq mer                                                                                                                                                                                                                                                                                     |                                          | Calls/Total<br>8.86%                                                                                           | BPC_valie<br>R[0]<br>R[1]<br>R[2]                                                                   | 1 0                                                                                                                      |

| X Disassembly<br>Disassembly          | [00000001] 00000<br>[00000002] 01200                                                                                                                                                         | ,                                                                                                                                | ×            | data mem (proq men<br>CLISA Operation Profile<br>+ Name                                                                                                                                                                                                                                                 |                                          | Calls/Total<br>8.86%<br>17.72%                                                                                 | BPC_valie<br>R[0]<br>R[1]<br>R[2]<br>R[3]                                                           | 1 0<br>0<br>0<br>3<br>9                                                                                                  |

| X Disassembly<br>Disassembly          | [00000001] 00000<br>[0000002] 01200<br>[00000003] 02200                                                                                                                                      | NOP<br>LDL R[2],#0<br>LDH R[2],#0                                                                                                | ×            | data mem & prog mer       CRLISA Operation Profile       + Name       + NOP       + decode       + B_type                                                                                                                                                                                               | e<br>Calis<br>7<br>14                    | Calls/Total<br>8.86%<br>17.72%<br>0.00%                                                                        | BPC_valie<br>R[0]<br>R[1]<br>R[2]<br>R[3]<br>R[4]                                                   | a 0<br>0<br>3<br>9<br>170                                                                                                |

| X Disassembly<br>Disassembly          | [00000001] 00000<br>[0000002] 01200<br>[00000003] 02200<br>[00000004] 01306                                                                                                                  | NOP<br>LDL R[2],#0<br>LDH R[2],#0<br>LDL R[3],#6                                                                                 | ×            | data mem & prog mer       CRLISA Operation Profile       + Name       + NOP       + decode       + B_type                                                                                                                                                                                               | e<br>Calis<br>7<br>14                    | Calls/Total<br>8.86%<br>17.72%<br>0.00%<br>0.00%                                                               | BPC_valie<br>R[0]<br>R[1]<br>R[2]<br>R[3]                                                           | a 0<br>0<br>3<br>9<br>170                                                                                                |

| X Disassembly<br>Disassembly          | [00000001] 00000<br>[0000002] 01200<br>[00000003] 02200<br>[00000004] 01306<br>[00000005] 02300                                                                                              | NOP<br>LDL R[2],#0<br>LDH R[2],#0<br>LDL R[3],#6<br>LDH R[3],#0                                                                  | ×            | data mem & prog mer       CPLISA Operation Profile       + Name       + NOP       + decode       + B_type       + D_type       + M_type                                                                                                                                                                 |                                          | Calls/Total 8.86% 17.72% 0.00% 0.00% 3.80%                                                                     | BPC_valie<br>R[0]<br>R[1]<br>R[2]<br>R[3]<br>R[4]                                                   | a 0<br>0<br>3<br>9<br>170                                                                                                |

| X Disassembly<br>Disassembly          | [0000001] 00000<br>[0000002] 01200<br>[00000003] 02200<br>[00000003] 01306<br>[00000005] 02300<br>[00000005] 00000                                                                           | NOP<br>LDL R[2],#0<br>LDH R[2],#0<br>LDL R[3],#6                                                                                 | ×            | data mem Aproq mer       CPLISA Operation Profile       + Name       + NOP       + decode       + B_type       + D_type       + M_type       + I_type                                                                                                                                                   | e<br>Calis<br>7<br>14                    | Calls/Total<br>8.86%<br>17.72%<br>0.00%<br>0.00%                                                               | BPC_valie<br>R[0]<br>R[1]<br>R[2]<br>R[3]<br>R[4]<br>R[5]                                           | 4 0<br>0<br>3<br>9<br>170<br>0<br>0                                                                                      |

| X Disassembly<br>Disassembly          | [0000001] 00000<br>[0000002] 01200<br>[00000003] 02200<br>[00000003] 01306<br>[0000005] 02300<br>[0000005] 02300                                                                             | NOP<br>LDL R[2],#0<br>LDL R[2],#0<br>LDL R[3],#6<br>LDH R[3],#0<br>NOP                                                           | ×            | data mem & prog mer       CPLISA Operation Profile       + Name       + NOP       + decode       + B_type       + D_type       + M_type                                                                                                                                                                 | Calls<br>7<br>14<br>Profiler             | Calls/Total<br>8.86%<br>17.72%<br>0.00%<br>0.00%<br>3.80%<br>5.06%                                             | BPC_valie<br>R[0]<br>R[1]<br>R[2]<br>R[3]<br>R[4]                                                   | 4 0<br>0<br>3<br>9<br>170<br>0<br>0                                                                                      |

| X Disassembly<br>Disassembly          | [0000001] 00000<br>[0000002] 01200<br>[0000003] 02200<br>[00000004] 01306<br>[00000005] 02300<br>[0000006] 00000<br>[0000006] 00000                                                          | NOP<br>LDL R[2],#0<br>LDH R[2],#0<br>LDL R[3],#6<br>LDH R[3],#0<br>NOP                                                           | ×            | Vata mem     A prog met       CPLISA     Operation       *     Name       *     NOP       *     decode       *     B_type       *     D_type       *     M_type       *     L_type       *     L_type                                                                                                   | rofiler                                  | Calls/Total<br>8.86%<br>17.72%<br>0.00%<br>3.80%<br>5.06%<br>0.00%                                             | BPC_valie<br>R[0]<br>R[1]<br>R[2]<br>R[3]<br>R[4]<br>R[5]                                           | 4 0<br>0<br>3<br>9<br>170<br>0<br>0                                                                                      |

| X Disassembly<br>Disassembly          | [00000001] 00000<br>[0000002] 01200<br>[00000003] 02200<br>[00000004] 01306<br>[00000005] 022300<br>[00000006] 000000<br>[00000007] 00000<br>[00000007] 1b324                                | NOP<br>LDL R[2],#0<br>LDH R[2],#0<br>LDL R[3],#6<br>LDH R[3],#0<br>NOP<br>NOP<br>MAC R[4],R[3],R[2]                              | ×            | Value     Aprog med       CPLISA Operation Profile       + Name       + NOP       + decode       + B_type       + D_type       + M_type       + I_type       + R_type       + Atype       + Atype                                                                                                       | g 0<br>ing 0                             | Calls/Total<br>8.86%<br>17.72%<br>0.00%<br>0.00%<br>3.80%<br>5.06%<br>0.00%<br>0.00%                           | ppc_valid           R[0]           R[1]           R[2]           R[3]           R[4]           R[5] | a 0<br>0<br>3<br>9<br>170<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0      |

| Disassembly     Disassembly     Symbo | [0000001] 00000<br>[0000002] 01200<br>[0000003] 02200<br>[0000003] 02200<br>[0000005] 02300<br>[0000006] 00000<br>[0000006] 15324<br>[0000000a] 15324<br>[0000000b] 15324                    | NOP<br>LDL R[2],#0<br>LDH R[2],#0<br>LDH R[3],#6<br>LDH R[3],#0<br>NOP<br>NOP<br>MAC R[4],R[3],R[2]<br>MAC R[4],R[3],R[2]<br>NOP | ×            | Verticate     Aprogram       CPLISA Operation Profile       +     Name       +     NoP       +     decode       +     B_type       +     D_type       +     M_type       +     M_text | g 0<br>ing 0                             | Calls/Total<br>8.86%<br>17.72%<br>0.00%<br>0.00%<br>3.80%<br>5.06%<br>0.00%<br>0.00%<br>0.00%                  |                                                                                                     | a 0<br>0<br>0<br>3<br>9<br>170<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 |

| X Disassembly<br>Disassembly          | [0000001] 00000<br>[0000002] 01200<br>[0000003] 02200<br>[0000003] 02200<br>[0000005] 02300<br>[0000005] 02300<br>[0000005] 00000<br>[0000007] 00000<br>[00000008] 1b324<br>[00000009] 1b324 | NOP<br>LDL R[2],#0<br>LDL R[3],#6<br>LDH R[3],#6<br>LDH R[3],#0<br>NOP<br>NOP<br>MAC R[4],R[3],R[2]<br>MAC R[4],R[3],R[2]        | ×            | data mem & proq med       CPLISA Operation Profile       * Name       * NOP       * decode       * D_type       * M_type       * Mirect_addressin       * indirect_addressin       * indirect_addressin                                                                                                 | g 0<br>ing 0                             | Calls/Total<br>8.86%<br>17.72%<br>0.00%<br>0.00%<br>3.80%<br>5.06%<br>0.00%<br>0.00%<br>0.00%<br>3.80%<br>.80% | ppc_valid           R[0]           R[1]           R[2]           R[3]           R[4]           R[5] | a 0<br>0<br>3<br>9<br>170<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0      |

# **Conclusion & Future Work**

- We have implemented in C++ and validated a working prototype of a quantum computer simulator that uses only linear space.

- This tool can be useful to help students & researchers validate quantum algorithms.

- □ Online resources at <u>http://www.eng.fsu.edu/~mpf/SEQCSim</u>

- □ Contact <u>michael.patrick.frank@gmail.com</u> for source code

- A future version will provide a more expressive quantum programming language based on C++.

- □ We are also designing an FPGA-based hardware implementation to boost simulator performance.

- This approach is made much more feasible by the extreme memory-efficiency of our algorithm.